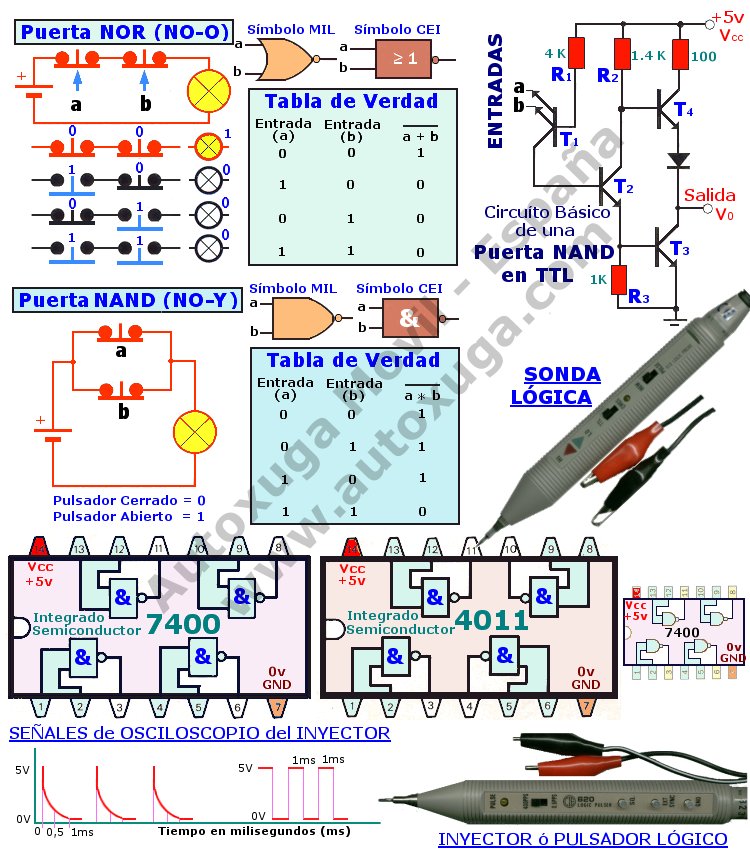

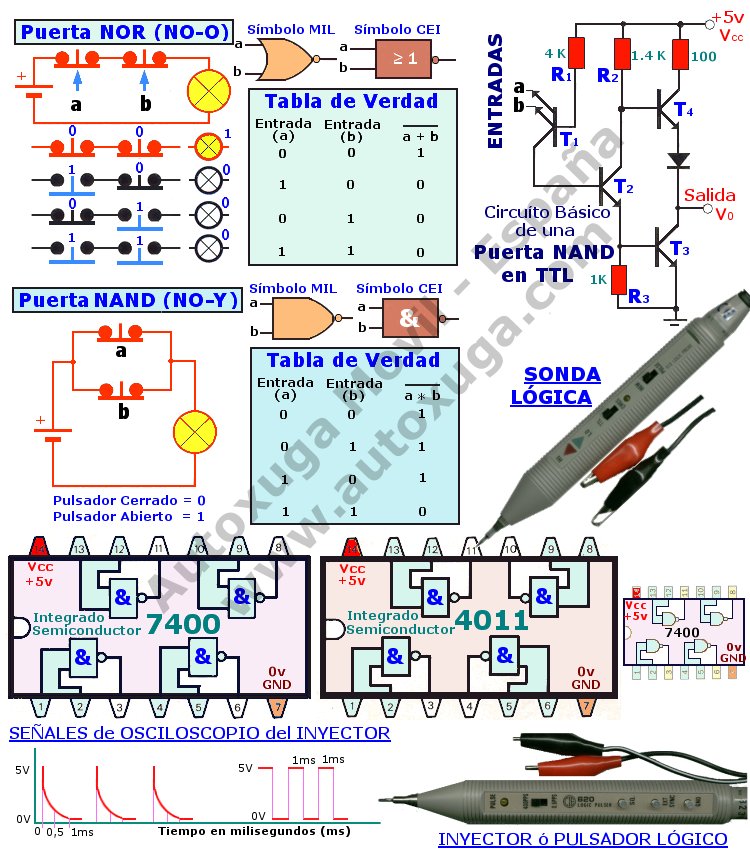

Para no sustituir piezas por simple rutina ó inercia, es conveniente conocer el funcionamiento básico de algunos Circuítos Integrados Digitales porque generalmente los Aparatos de Diagnosis que se conectan a las UCEs detectan FALLOS que en muchos casos no existen. Las Puertas NOR y NAND y sus TABLAS de VERDAD están sacadas de los Programas Informáticos de SIMULACIÓN de AUTOXUGA, y se explican brevemente para que se adquiera un conocimiento básico sobre el tema.

Realmente las TABLAS de VERDAD mostradas y las Puertas NOR y NAND no se corresponden con INTERRUPTORES, sino que son circuítos construídos con TRANSISTORES tal como el representado en el lado derecho, aunque el resultado de su funcionamiento se entiende mejor con Interruptores.

Integrados 7400 y 4011 de Puertas NAND según CEI y MIL:

Ambos Integrados son similares físicamente, pero el funcionamiento de sus Circuítos va a ser distinto. Los INTEGRADOS de la izquierda (7400 y 4011) están dibujados según Normas CEI y el de la derecha (7400) según las MIL.

La alimentación de Tensión en ambos INTEGRADOS la recibe la Patilla 14, y la Masa, la 7. Para hacer una PRUEBA de FUNCIONAMIENTO, por ejemplo, en el 4011, debe INYECTARSE una señal con el Inyector Lógico por las Patillas 12 y 13, y por la 11 se observa en la Sonda Lógica si se recibe la señal INYECTADA en esa NAND. Las otras Puertas se verifican de la misma manera.

Cálculo sencillo del Circuíto de Puertas NAND en TTL:

Si una de las ENTRADAS (a ó b) está a NIVEL LÓGICO 0 (por ejemplo 0,2v), la unión B-E de dicha ENTRADA está polarizada directamente, siendo la Corriente de Colector de T1 muy pequeña, y la Corriente de Base:

Iß1 = VR1/R1 = Vcc - V(B-E) - Vi/R1 = 5 - 0,6 - 0,2/4000 = 1 mA

De esta manera, la Tensión en el Colector del Transistor T1 es de unos 0,4v:

Vi + V(C-E)sat = 0,2 + 0,2 = 0,4 v

La Tensión de 0,4 v es INSUFICIENTE para que T2 y T3 conduzcan, ya que necesitan al menos 1,2 v; y al estar T2 cortado, son NULAS sus Intensidades de Colector y Emisor.

Si las ENTRADAS (a y b) están a NIVEL ALTO (1), las uniones B-E del Transistor T1 están inversamente polarizadas, mientras que la unión B-C del mismo Transistor está polarizada directamente, provocando que el Transistor T2 reciba Corriente de Base, a través de R1, y se sature, y la Intensidad de Emisor de este último Transistor provocará en R3 la suficiente caida de Tensión (aprox 0,7v) para saturar a T3, haciendo que la Tensión de salida esté a un Nivel Bajo V(C-E3)sat = 0,2v. Los Programas Informáticos de AUTOXUGA para SIMULAR CIRCUÍTOS muestra todo lo anterior de manera sencilla.